reSPACE

Reconfigurable Signal Processing and Classification Environment

| Keywords: | Machine Learning, Signal Processing, Parallelization, FPGA, Embedded Systems |

| Status: | active |

| Operating system: | Linux |

| Programming languages: | Python, C, Matlab, VHDL |

| Licence: | Proprietary |

| Ownership: | This software was developed by the DFKI as well as by the Robotics Research Group and the University of Bremen and is being further developed under this responsibility. For questions and suggestions, please refer to the contact persons. |

Software description

Exploiting the Advantages of FPGAs for Mobile and Embedded Signal Processing

Intelligent mobile or embedded systems like robots usually require high-dimensional and realtime-capable signal processing and machine learning. To achieve this, the processing requires to be powerful and energy efficient at the same time. Field-Programmable Gate Arrays (FPGAs) are well suited to meet these requirements. Recent FPGA-models include a high number of programmable logic-cells and special resources for signal processing. Additionally, some of these chips feature complete CPU cores, which allow it to run operating systems and complex software applications.

Software-Hardware Partitioning

Applications that utilize signal processing and machine learning can often be divided into computationally expensive parts, which should be mapped to an FPGA, and more high-level management tasks, which should be mapped to a CPU. reSPACE allows to implement the computationally expensive parts on an FPGA by utilizing a model-based development process.

Hardware Dataflow Accelerators

reSPACE is based on static heterogeneous dataflow computing: an application specific dataflow hardware accelerator can be implemented by combining a set of different predefined compute nodes. Every node performs a single transformation on the data. All nodes can operate in serial or parallel. The nodes and the hardware accelerator are purely data-driven and can, therefore, operate independent from the CPU. The final hardware accelerator can be easily integrated into an FPGA-based System on Chip, all required software components, i.e., device drivers and interface libraries, are automatically generated by reSPACE.

Combination with pySPACE

reSPACE can be easily combined with pySPACE. Accordingly, the evaluation and data management functionality of pySPACE can be used to evaluate the hardware system.

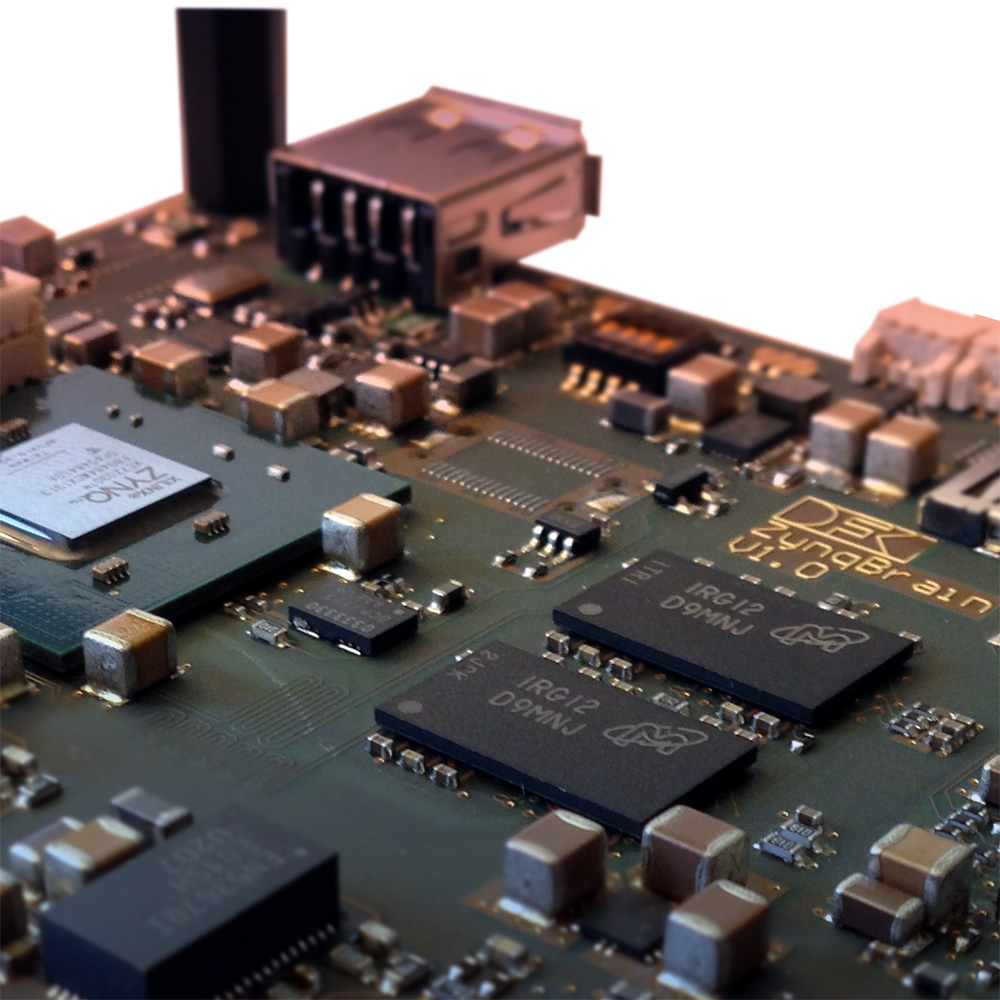

Example Application Platform: ZynqBrain

The ZynqBrain electronics board, which contains a Xilinx Zynq® EPP and miscellaneous interfaces, was developed at the DFKI RIC as a central electronics component for various robots and a special purpose platform for signal processing. The ARM® CPU can be used to, e.g., run pySPACE as a high level application, while the computationally expensive parts are mapped to the FPGA-based dataflow accelerators that are implemented using reSPACE.

Videos

IMMI: Adaptation of a man-machine interface for multi-robot control with respect to task engagement using embedded Brain Reading

The video shows a man-machine interface for multi robot control that is adapted online with respect to task load and task engagement to improve user support and efficiency of interaction by means of embedded Brain Reading (eBR). The level of task engagement is inferred from the single-trial detectability of P300-related brain activity with the need for a secondary task to measure task load.