POMAA

Pareto-Optimaler MAchine Learning ASIC

Ziel von POMAA ist die Entwicklung eines hybriden ASICs in 22FDX/FDSOI-Technologie, bestehend aus einem RISC-V-Prozessorkernes für die Unterstützung von Software-Komponenten und einem applikationsspezifischem Machine-Learning-IP Core (ML-IP), welcher für die rechenintensiven Teile des Systems genutzt wird, insbesondere für Verfahren basierend auf tiefen neuronalen Netzen/Deep Learning. Das zugrundeliegende ASIC-Design wird mittels der Features der FDSOI-Technologie auf maximale Energieeffizienz ausgelegt.

| Laufzeit: | 01.10.2019 bis 30.09.2020 |

| Zuwendungsempfänger: | Universität Bremen |

| Anwendungsfelder: | Datenmanagement |

Projektdetails

Ein wesentliches Problem bei der Verwendung von KI ist der große Bedarf an schneller und effizienter Hardware. Aktuelle Methoden des maschinellen Lernens, insbesondere tiefe neuronale Netze, basieren im Allgemeinen auf rechenaufwändigen numerischen Verfahren. Der dadurch entstehende Rechenaufwand ist insbesondere dann kritisch, wenn die KI bzw. ML-Methoden in miniaturisierten und ggf. eingebetteten Systemen verwendet werden sollen, da in diesem Fall sowohl die zulässige physische Größe und der Energieverbrauch möglichst gering sein müssen. Ein möglicher Ansatz ist hierbei die Verwendung von hochspezialisierter Hardware, z.B. in Form eines ASICs für das maschinelle Lernen. Gerade bei diesen sich widersprechenden Anforderungen – hohe Leistungsfähigkeit und Genauigkeit einerseits, geringer Energieverbrauch andererseits – ist es jedoch auch notwendig, nicht nur eine nach einem einzelnen Kriterium optimierte Hardware zu verwenden, sondern verschiedene Kriterien anzulegen und ein im Hinblick auf verschiedene Kriterien Pareto-Optimalen Systems zu entwickeln. Optimaler Weise bietet ein solches System nicht nur ML-spezifische Funktionalität, sondern auch Unterstützung klassischer software-spezifischer Funktionen, um für unterschiedliche Aufgaben einsatzbar zu sein.

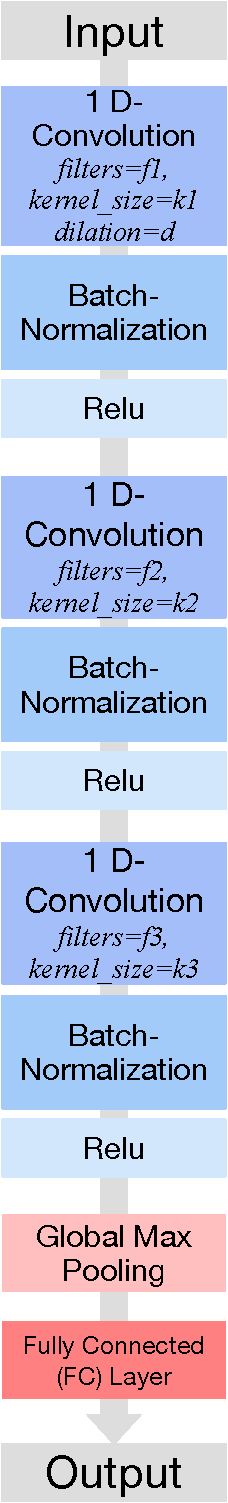

Um die bestmögliche Hardwarearchitektur für ein energieeffizientes KI-System zu entwickeln, ist sowohl eine Optimierung der Hardware als auch eine effiziente Architektur der neuronalen Schichten notwendig. Eine hybride, beidseitige Optimierung verspricht hier die beste Energieeffizienz bei verlangter (Klassifikations-)Performanz. Hierzu strebt POMAA zwei Optimierungen in einer Schleife an. Basierend auf einer initialen Analyse der zugrundeliegenden Daten und Aufgabenstellung des Wettbewerbs wird eine automatisierte Generierung und Selektion von NN-Architekturen durchgeführt. Diese Architekturen können sich sehr in den Schichten (Art, Anzahl Neuronen, etc.) unterscheiden und liefern für die Daten die benötigte Klassifikationsperformanz bei minimaler Anzahl an Parametern. In bestimmten Fällen lassen sich NN-Schichten in dieser Phase des ML-Designs durch Signal/Vorverarbeitungsmethoden ersetzen. Diese Menge von Architekturen wird synthetisiert und deren Energieeffizienz und Lastprofile per Simulation ermittelt. Basierend auf diesen Ergebnissen wird eine neue Zielfunktion automatisch adaptiert und mit ML- Methoden optimiert, die besonders auf die Auswertung teurer Zielfunktionen ausgelegt sind, um neue Architekturen zu optimieren und wieder zu synthetisieren. Dieser Prozess wird durchlaufen, bis der geringstmögliche Energieverbrauch erzielt worden ist.